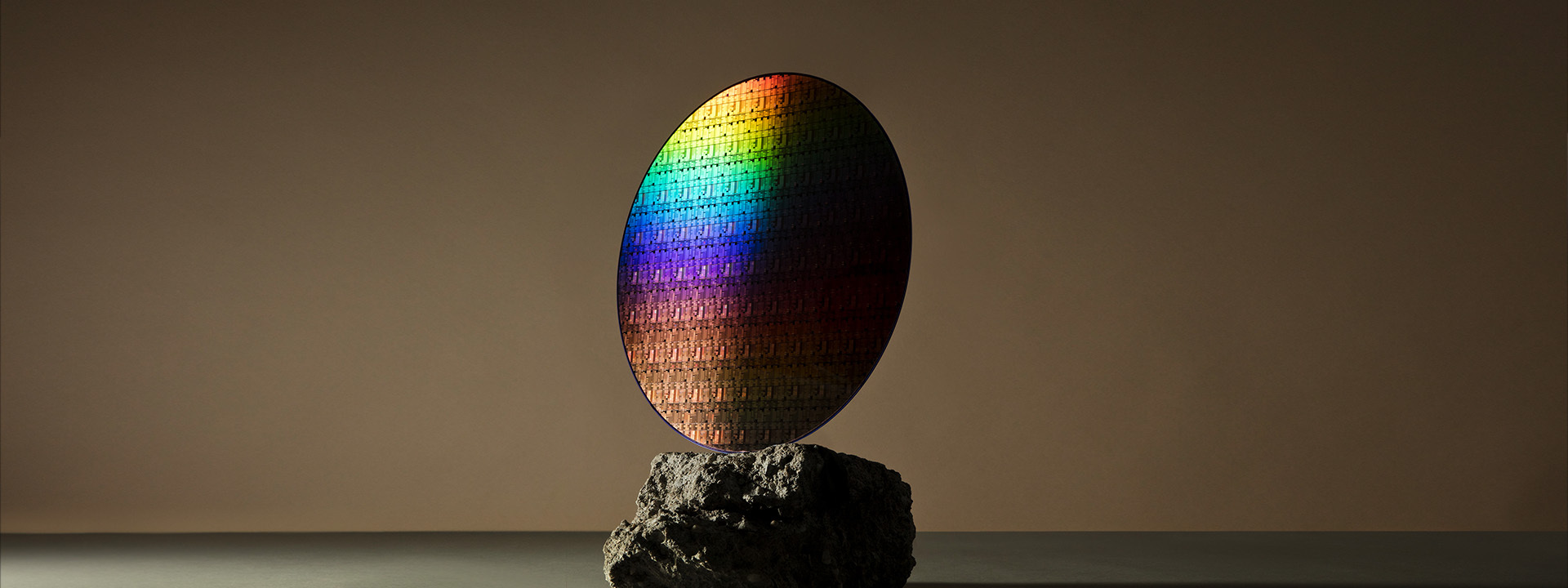

Samsung and IBM, two leaders in semiconductor design, have presented a ground-breaking new vertical transistor architecture that may turn processors from rectangular slabs to cubes.

The idea of this novel approach is to increase the semiconductor’s performance, improve the energy flow, and lay a path to scale beyond nanosheet fabrication levels, which would reduce the energy required for the unit to operate by up to 85%.

By scaling processors down at that level, IBM and Samsung would introduce game-changing technology in the following sectors:

- Smartphone batteries would last for over a week on a single charge

- Laptops and tablets won’t get as hot since the waste of energy will be reduced

- Cryptomining and data encryption operations would cost a lot less to carry out

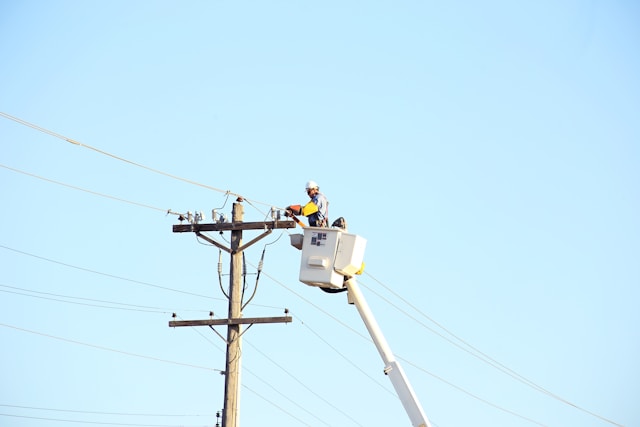

- Supercomputers would require significantly less electric power to operate

- Internet of Things (IoT) tech would expand to tiny devices using smaller button batteries

The above are just some examples, as autonomous vehicles or even spacecraft would benefit greatly from the vertical semiconductor design.

To achieve all that, the firms used a fabrication technology that positions transistors perpendicularly to the surface of the chip, allowing a vertical current flow. The apparent advantage of this approach is the ability to pack a larger number of transistors into a given space.

For starters, Samsung will produce these chips using its 5 nm node lines, and IBM will deploy them on its own server platforms. It is estimated that by 2025, the chip production will pass to the 2 nm technology, which IBM developed and presented in May 2021. Those chips can cram 50 billion transistors in a space the size of a fingernail, so when combined with the vertical design technology, the results are expected to be at an entirely new level.