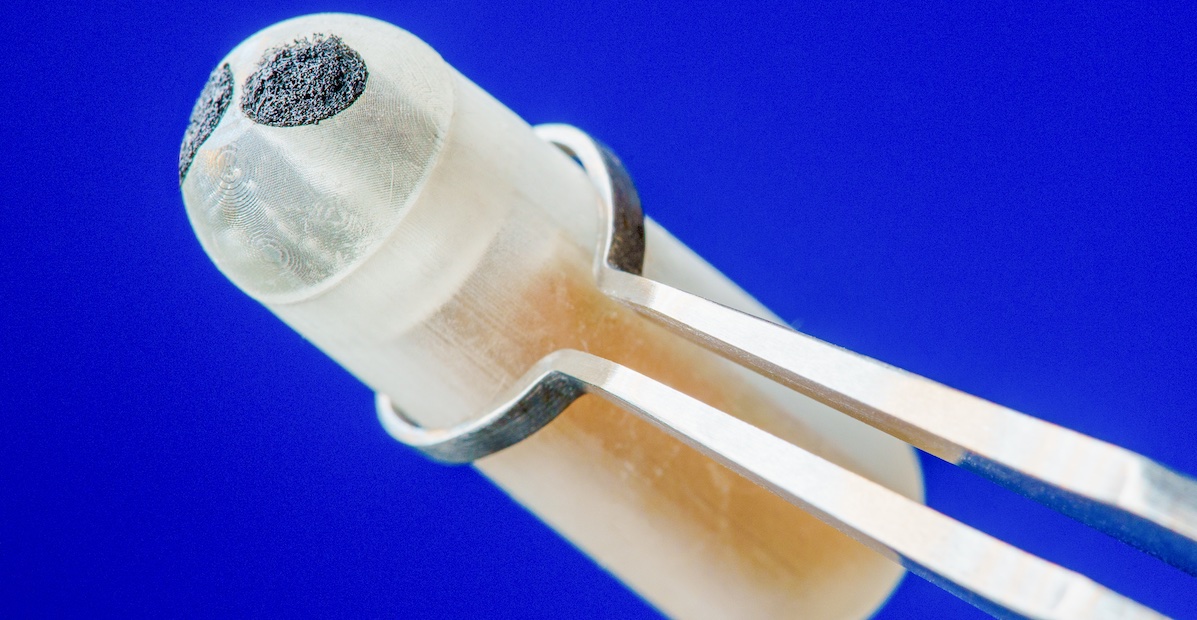

The lowRISC Community Interest Company (CIC) and the OpenTitan Coalition have announced their historic milestones by producing the world’s first commercial silicon chip that includes open-source, built-in hardware security. The success is the result of support and investment by the nine coalition members, including Google, Winbond, Nuvoton, zeroRISC, Rivos, Western Digital, Seagate, ETH Zurich, and Giesecke+Devrient, hosted by the non-profit lowRISC CIC, to bring first trustworthy, transparent, secure silicon platform to the market.

In 2018, Google launched the OpenTitan project together with the nonprofit lowRISC and its partners and this is the result of five years of collaboration. During its lifetime, the OpenTitan coalition has developed as an open silicon ecosystem.

As cyber threats continue to evolve, the need for robust hardware security solutions is more important, leading to the advent of the open-source security chip as a new player in the field of hardware security. Designed to enhance the security of electronic devices, the chip offers a promising approach to protect against cyber threats. This also presents another step in the growth of the open hardware movement, which has been increasingly developing since the born of the popular open-source processor architecture RISC-V.

OpenTitan has gone beyond RISC-V’s open-source instruction set, which gives openly available prescriptions for how a computer can operate efficiently at the most basic level, by delivering an open-source design for the silicon itself.

The first commercial silicon chip, called Earl Grey, is developed by using a RISC-V-based processor core, including several built-in hardware security and cryptography modules, all working together in a self-contained microprocessor. It uses a hardware security protocol known as a root of trust (RoT) as an idea to provide an on-chip source of cryptographic keys that is inaccessible remotely. Therefore, the system can trust that it hasn’t been tampered with, providing a basis to build security on.

In addition, openly accessible schematics and design files allow designers from all backgrounds to audit and test the RoT chips’ performance. In this way, they can also work together to solve the problem’s weak points. This on-chip security is also adopted in devices forming the Internet of Things (IoT), which often face unaddressed security challenges.